In 12 the authors presented a low to high voltage level shifter for use in a vlsi chip for mems applications.

A low voltage to high voltage level shifter circuit for mems application.

High voltage 15 v drivers are integrated into the vlsi chip for mems application with the development of soc technology.

The pre driver circuit which generates the pull up and pull down signal is mainly a voltage level shifter circuit.

Simulation result of the proposed voltage level shifter circuit.

The design uses a stack of.

The simulation result indicates that the magnitude of the vgs.

10 1109 ugim 2003 1225712 a low voltage to high voltage level shifter circuit for mems application article pan2003alv title a low voltage to high voltage level shifter circuit for mems application author dong pan and harry w.

The level shifter often consumes significant power due to high supply voltage and has limited bandwidth due to the low f t of thick oxide high voltage transistors.

Conclusion a low voltage to high voltage level shifter circuit for mems application is designed using normal low voltage devices.

The pre driver circuit which generates the pull up and pull down signal is mainly a voltage level shifter circuit.

The level shifter is a key circuit component in multi voltage circuits and has important implementation 15.

It features zero dc current consumption while reduces internal voltage swing.

A shifter circuit comprises in one embodiment an input voltage divider stage comprising multiple transistors arranged in a transistor stack defining a plurality of intermediate nodes.

Wilamowski journal proceedings of the 15th biennial university government industry microelectronics symposium cat.

This approach also requires dual supply voltages.

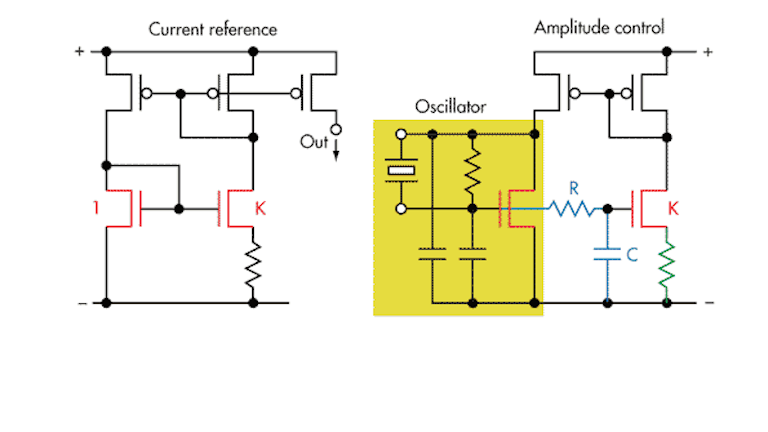

Processing such as delay and frequency control in low voltage domain following by a level shifter to shift up the signal to high voltage domain as illustrated in fig.

It converts the low voltage control signal to high voltage control signal.

Li and bogdan m.

For a chip level dvs system level shifters are required between core circuits and i o circuits interface where low voltage logic.

The transistor stack is connected between an input signal and ground and has at least one output.

The interface of a low voltage and high voltage gates.

Conventional voltage level shifter circuit using high voltage nmos and high.

An inverting buffer stage is connected to a supply voltage and coupled to the input voltage divider s output.

The pre driver circuit which generates the pull up and pull down signal is mainly a voltage level shifter circuit.